Lab 6 - EE 421L

Allis Hierholzer

hierholz@unlv.nevada.edu

10/24/18

Pre-Lab:

- Back-up all work from the lab and the course

- Go through Cadence Tutorial 4

- Read through the lab before starting to work on it

Lab Description:

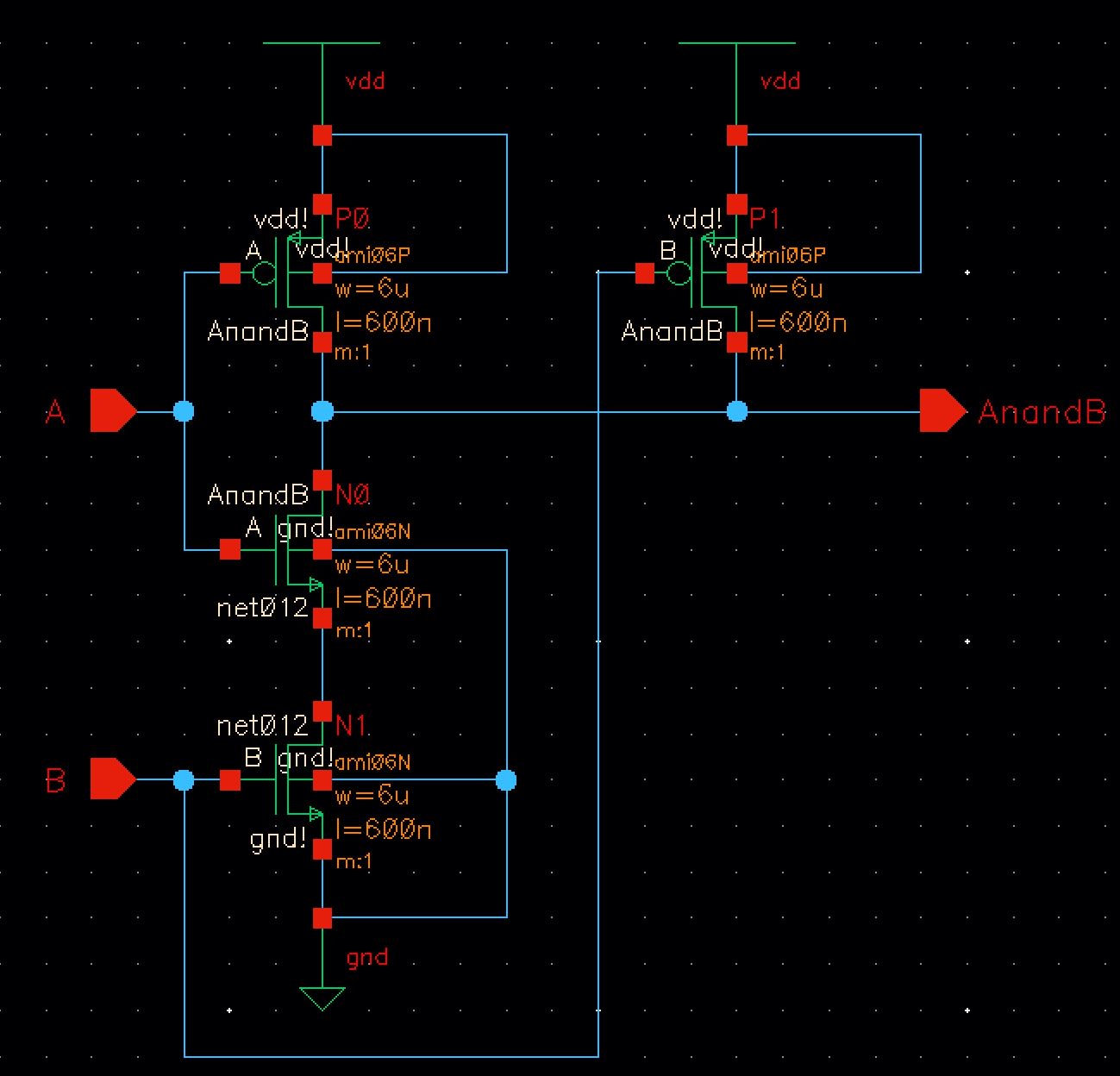

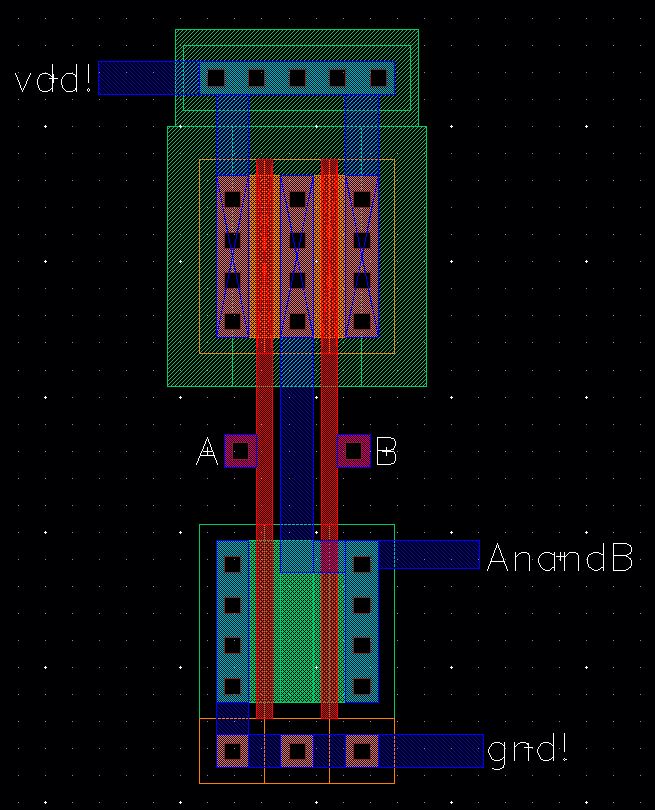

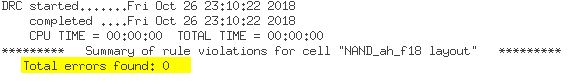

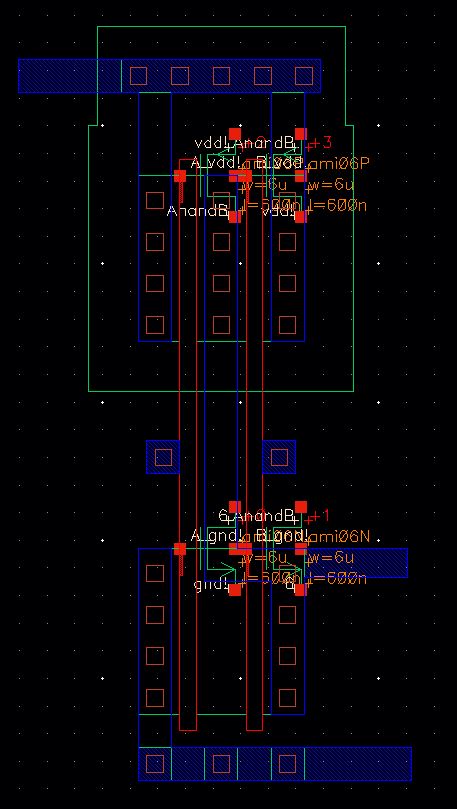

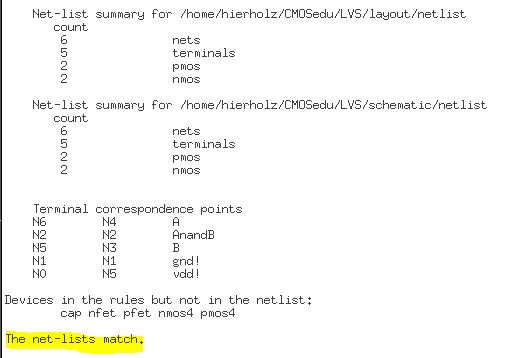

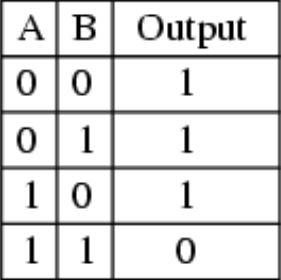

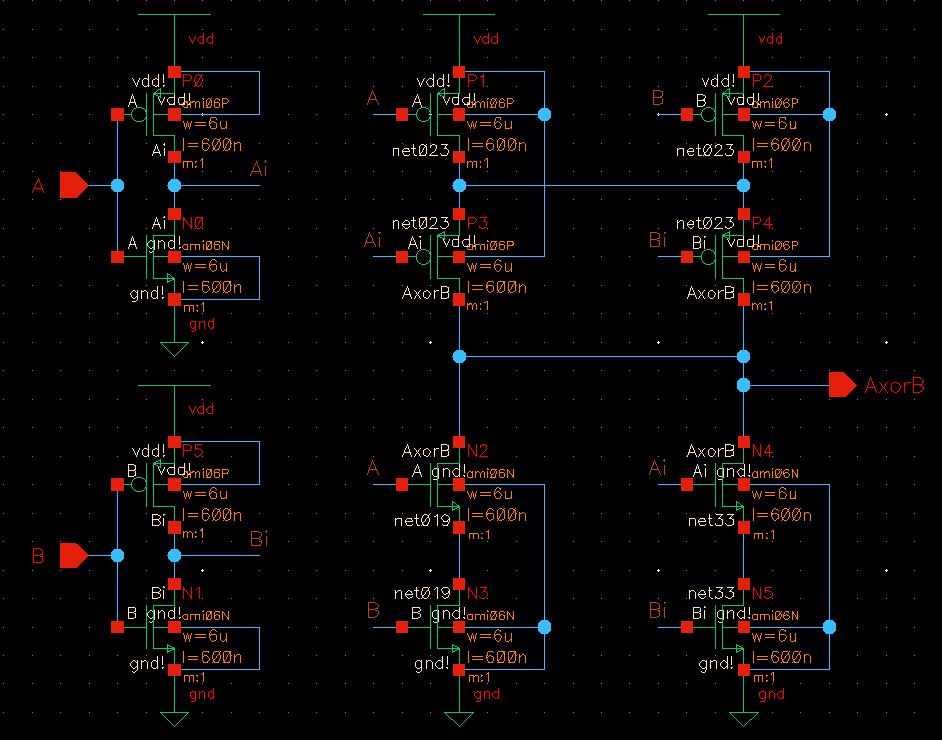

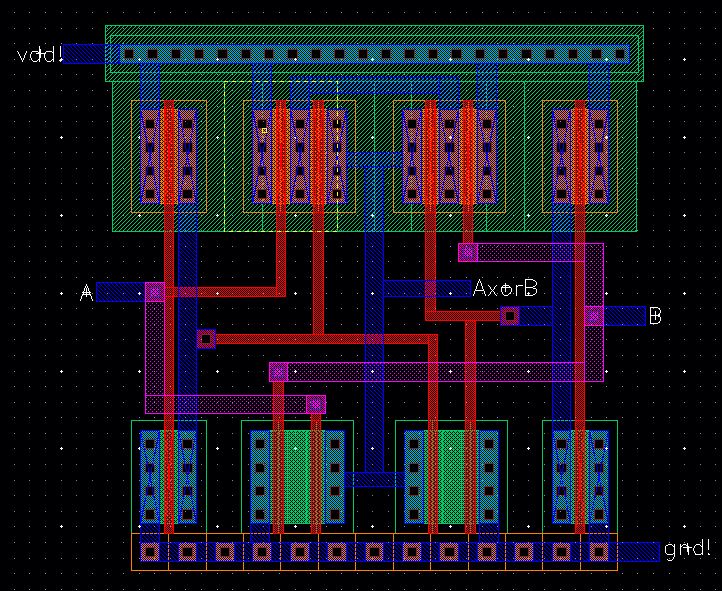

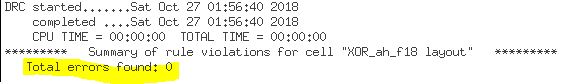

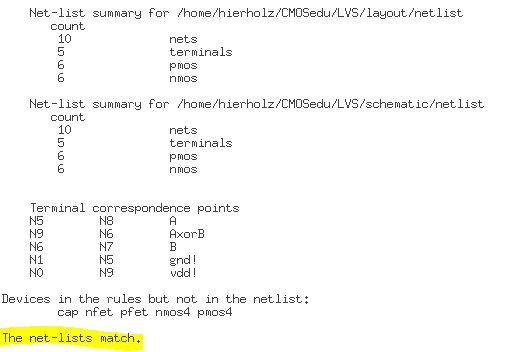

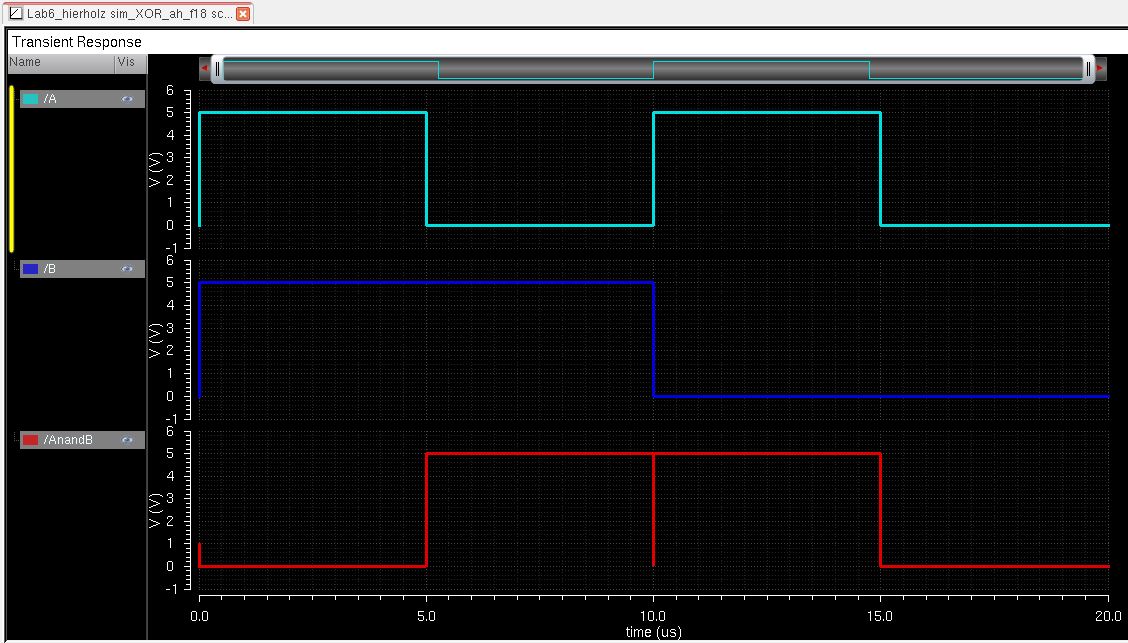

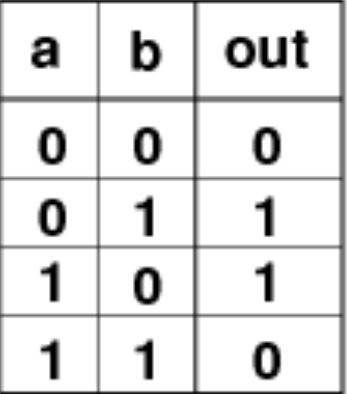

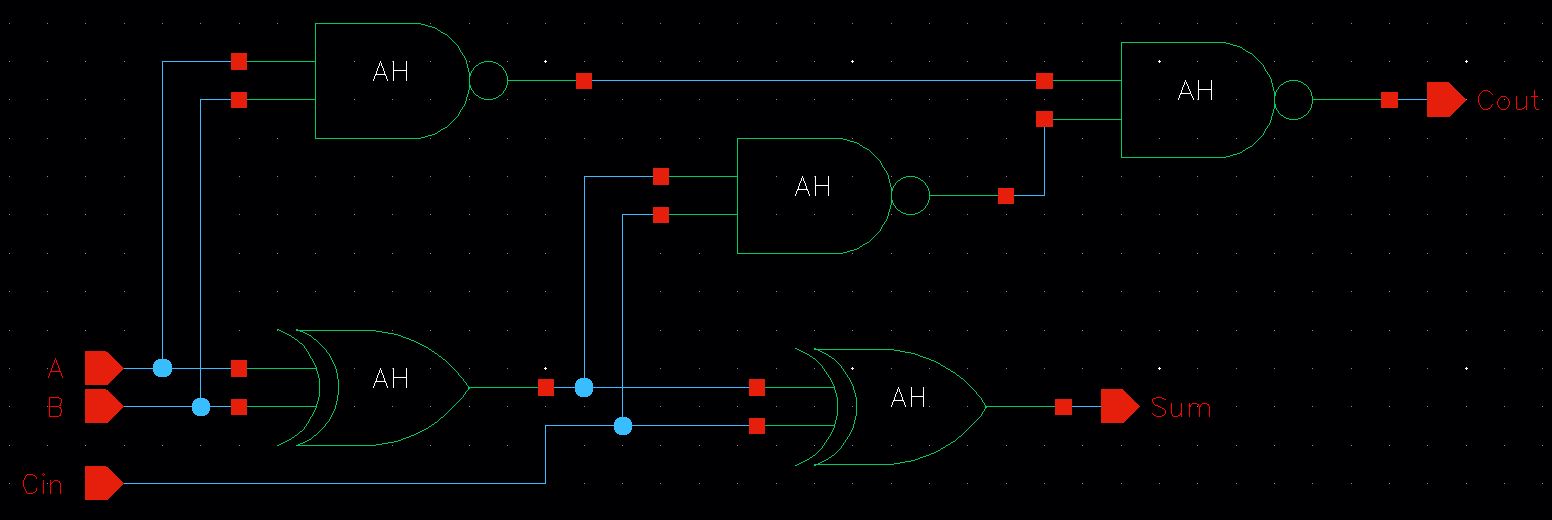

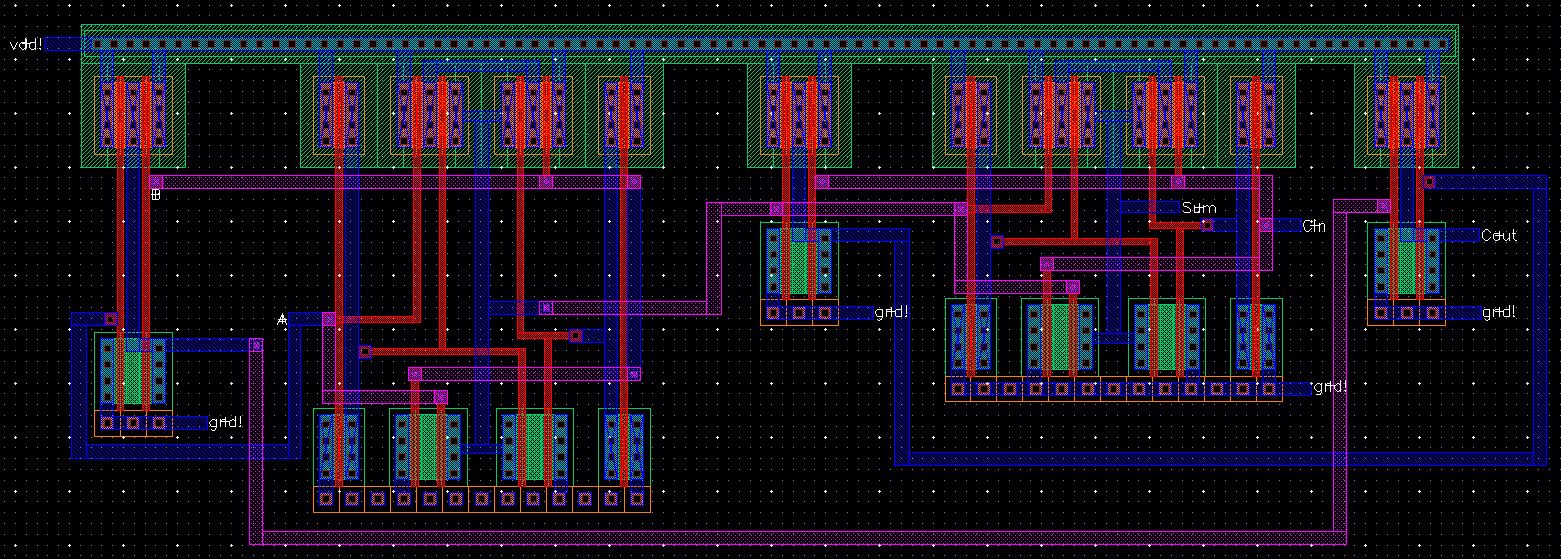

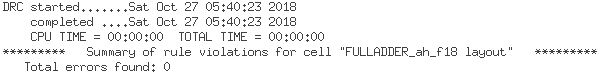

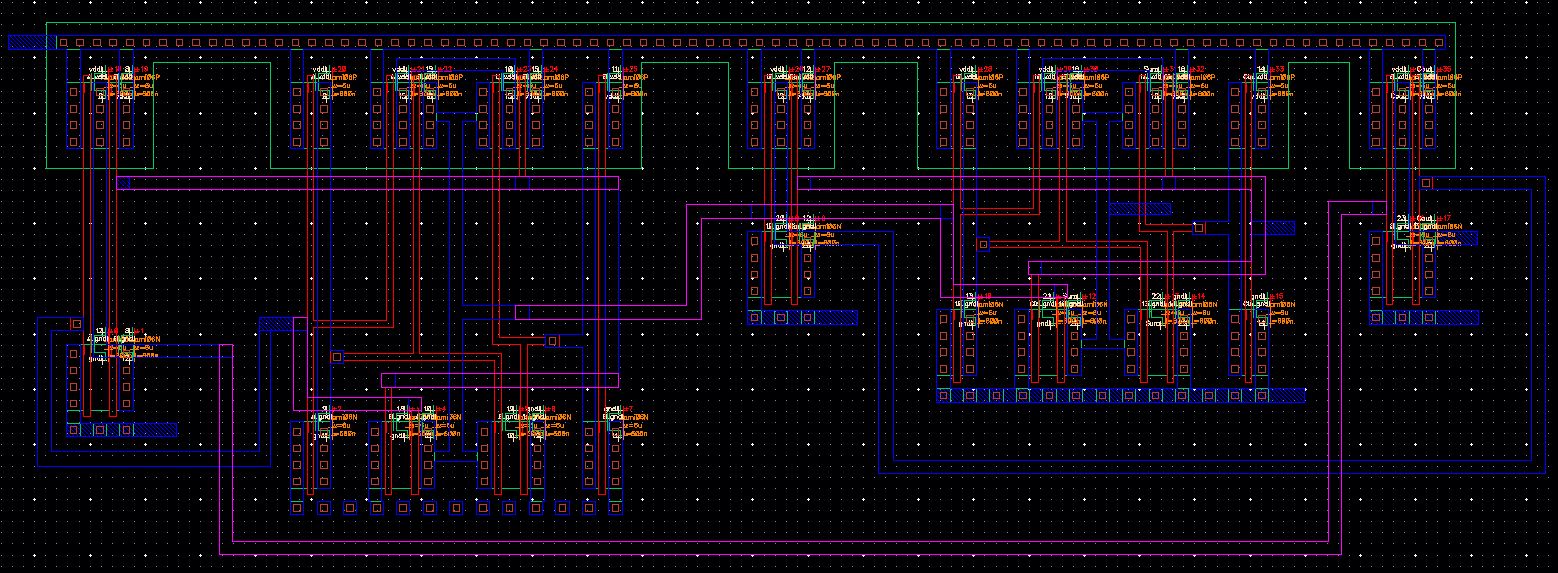

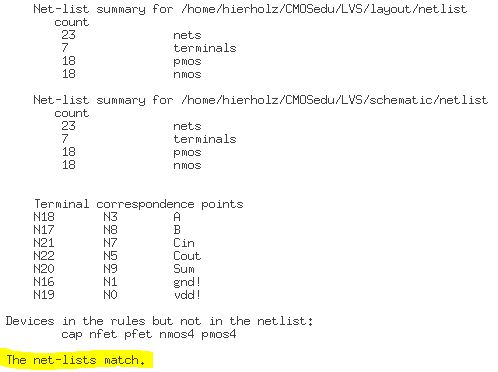

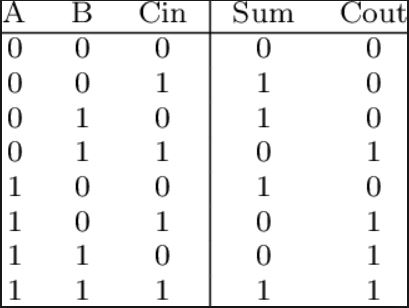

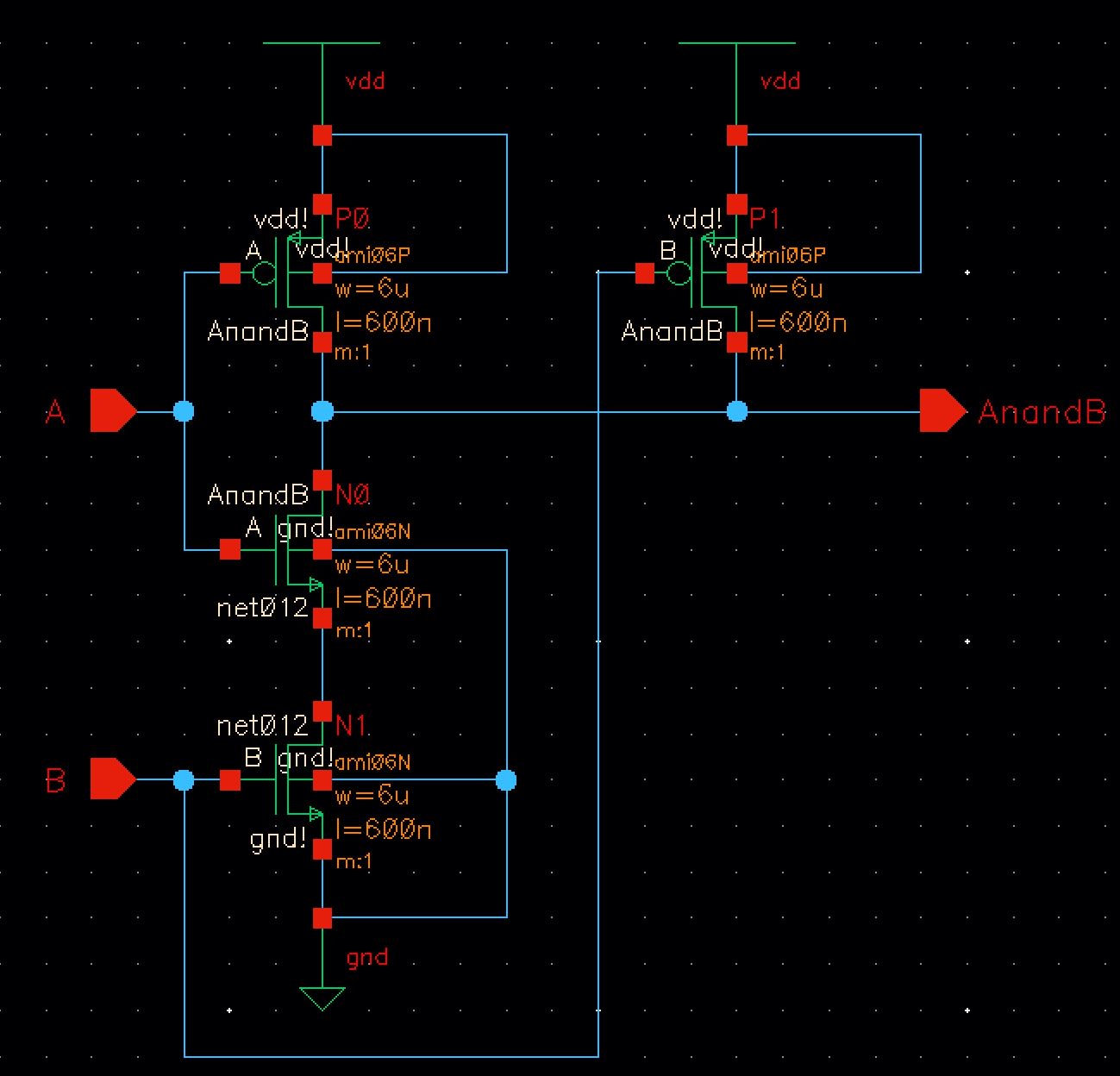

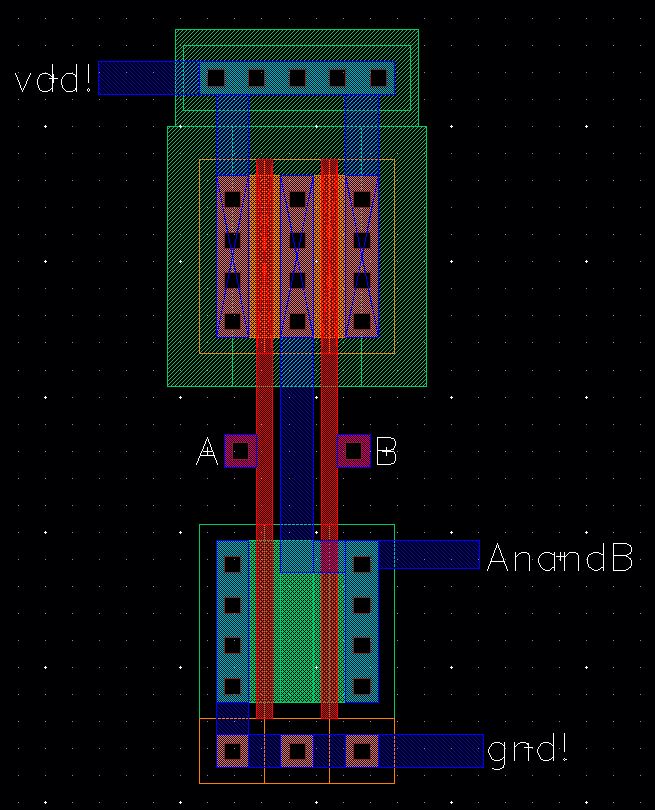

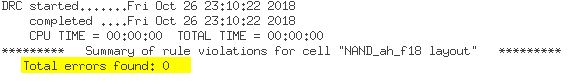

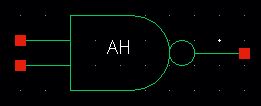

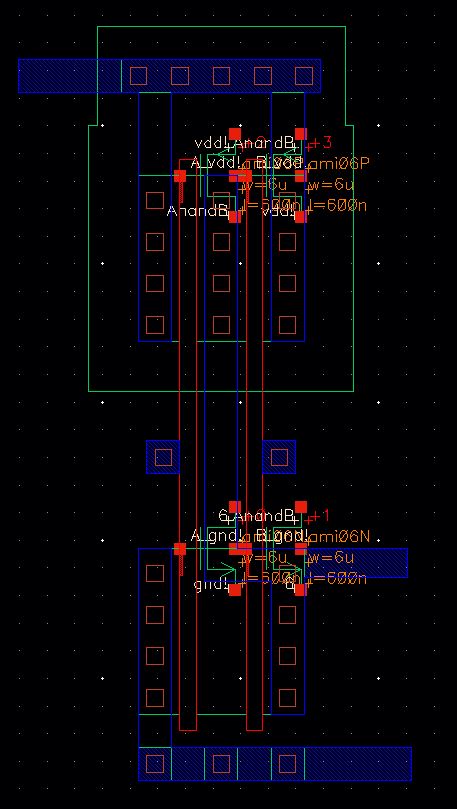

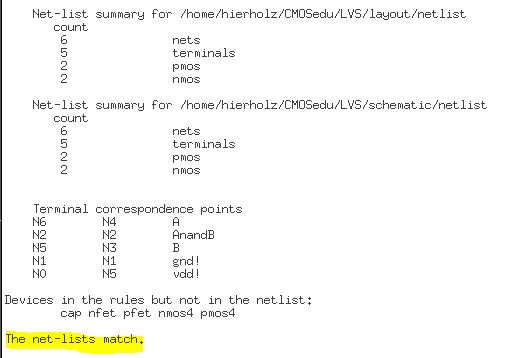

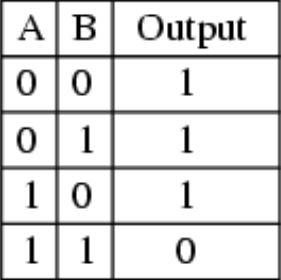

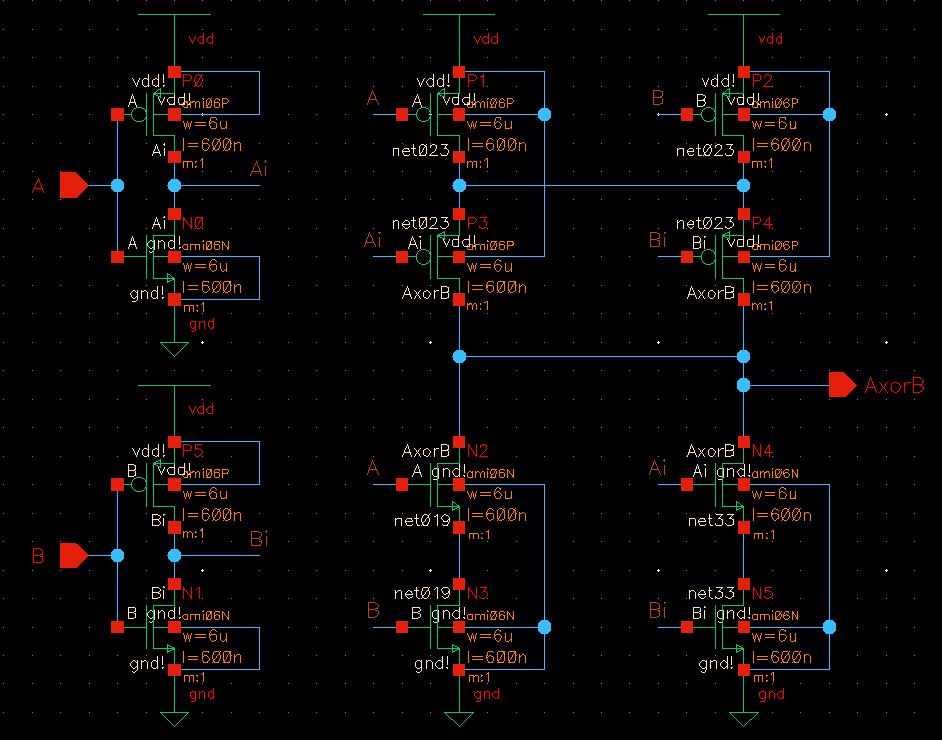

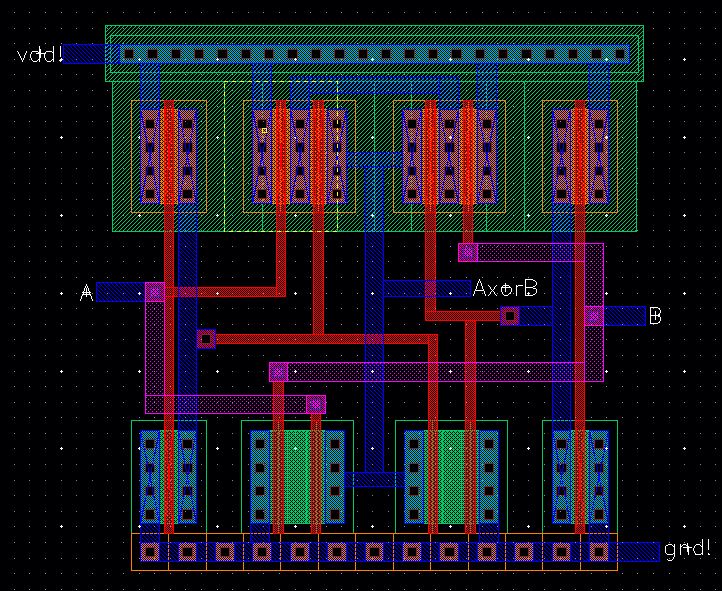

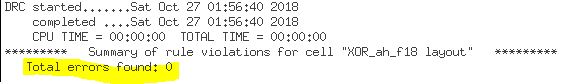

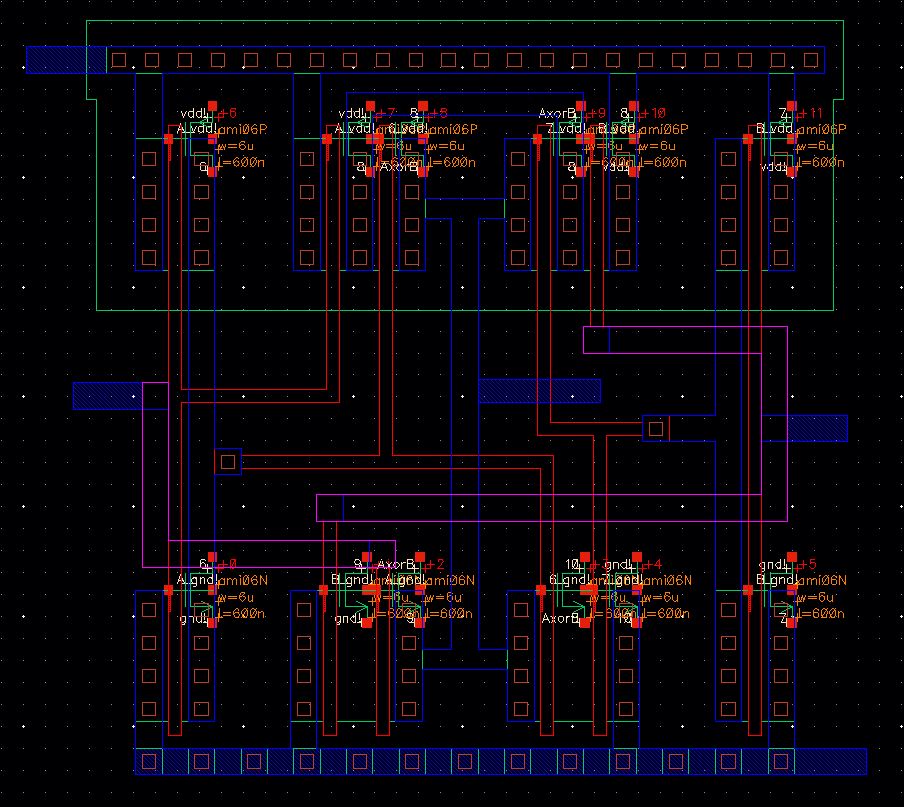

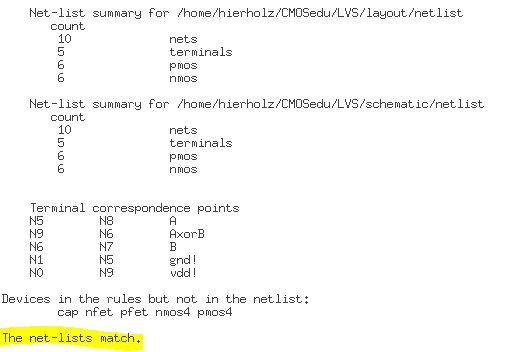

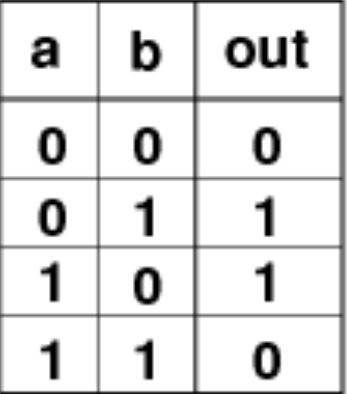

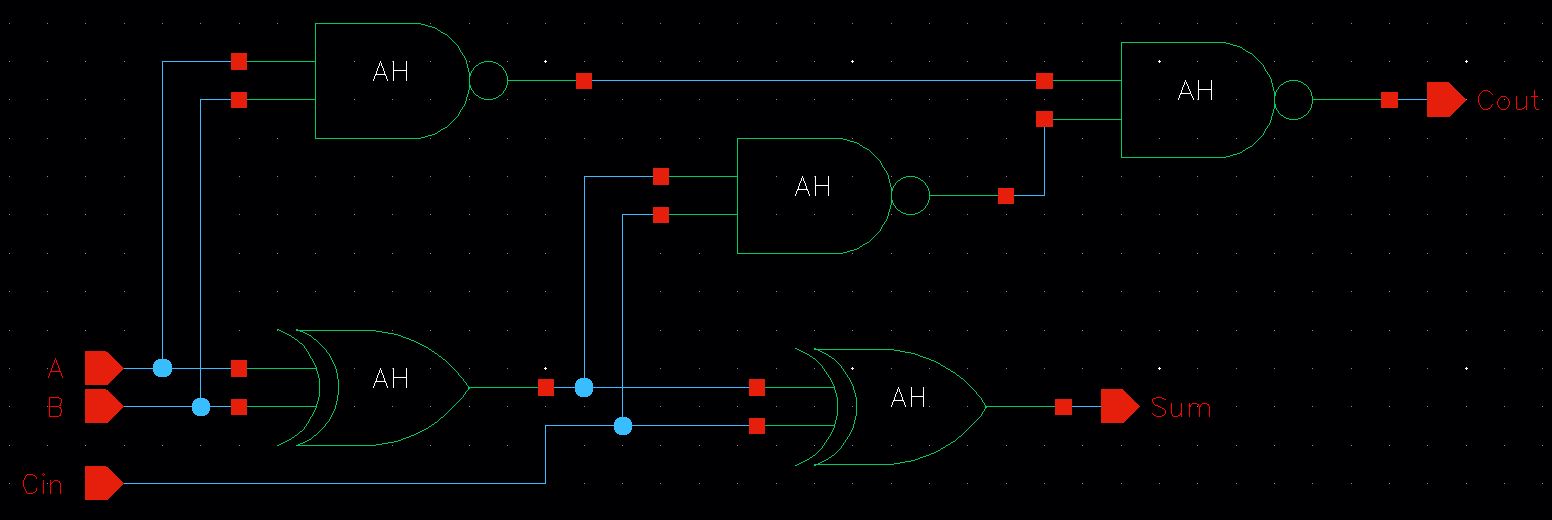

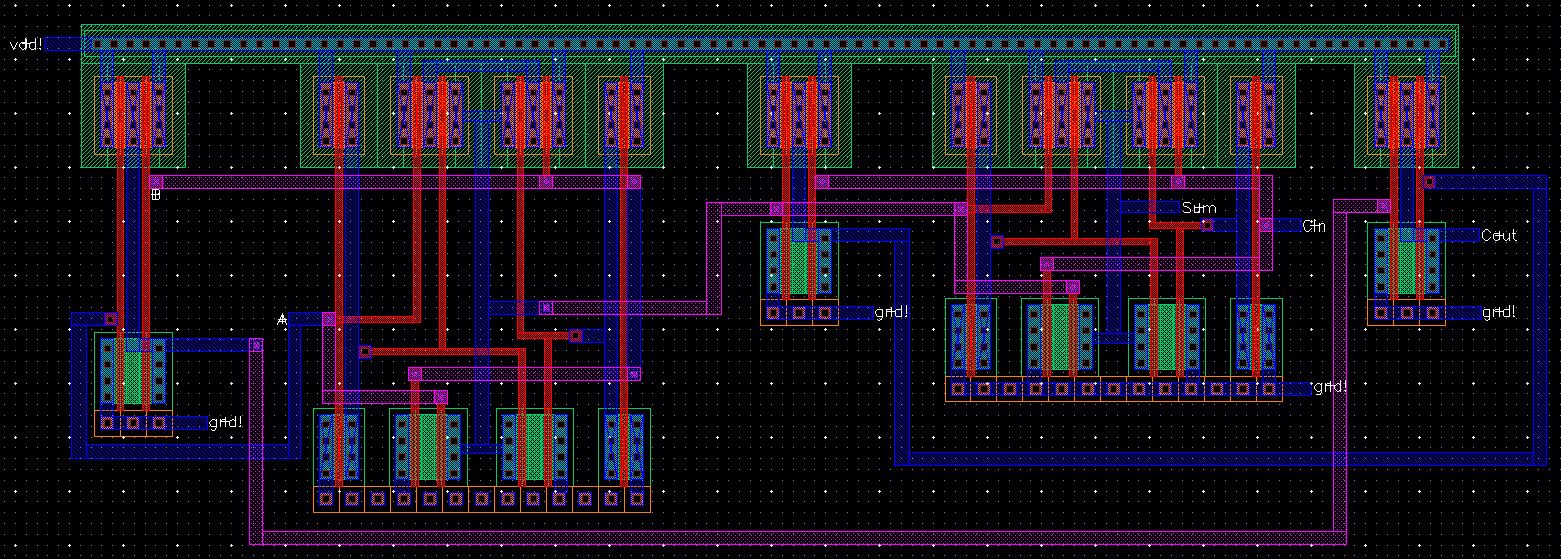

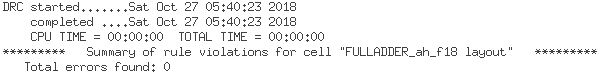

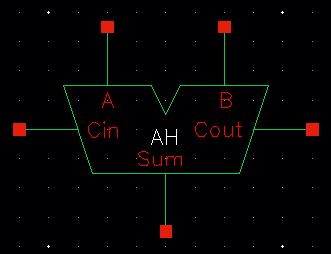

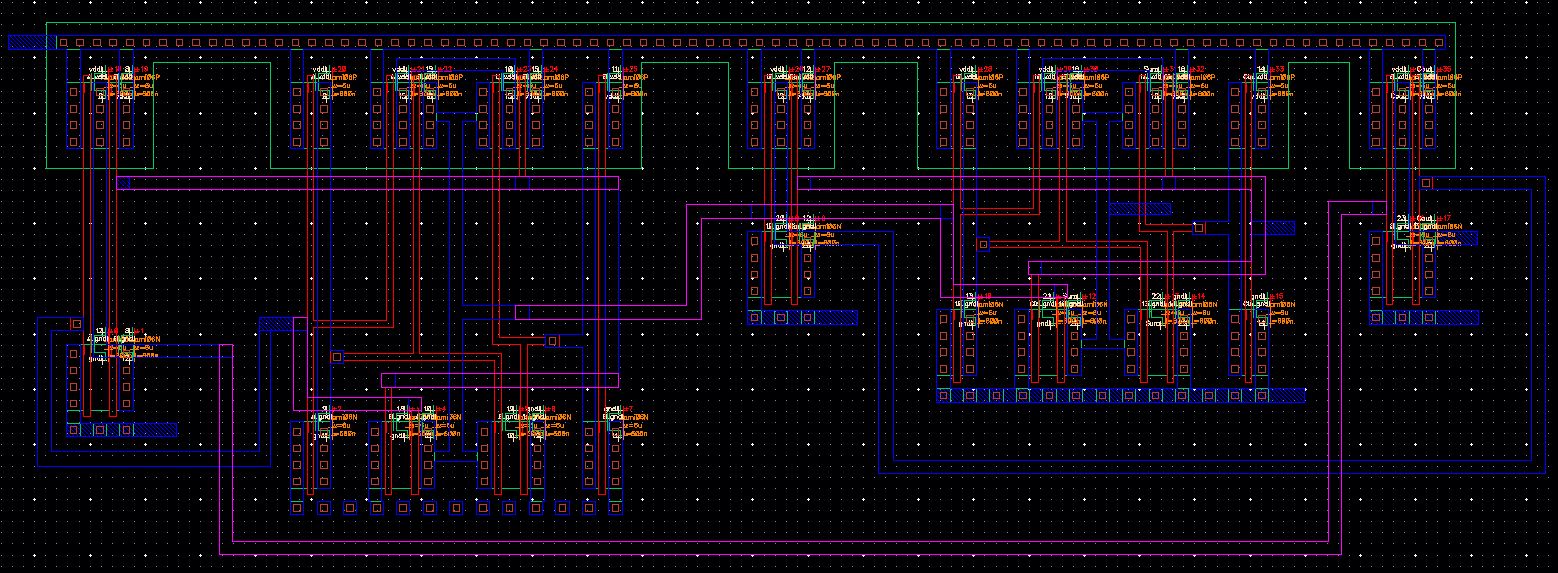

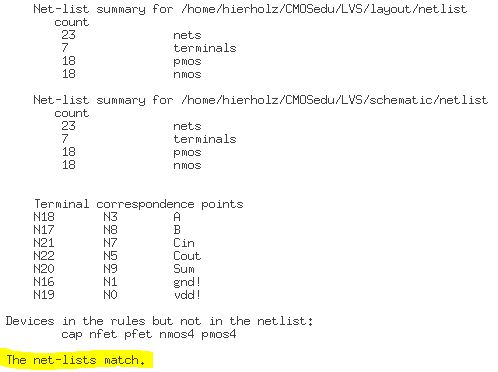

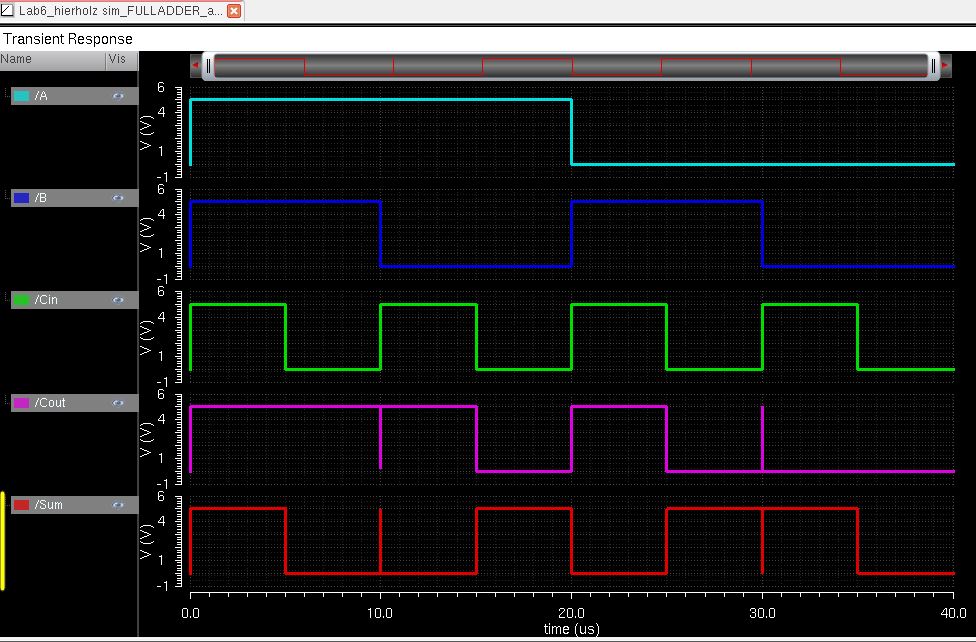

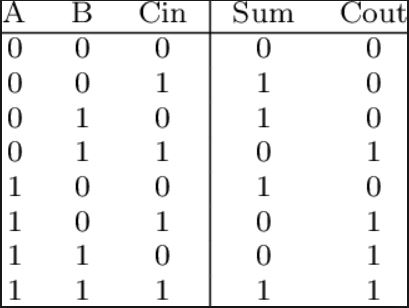

- This lab focuses on designing a layout of a CMOS NAND gate, XOR gate, and a full adder and running its simulation

- Create

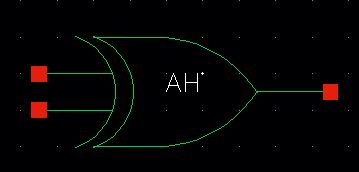

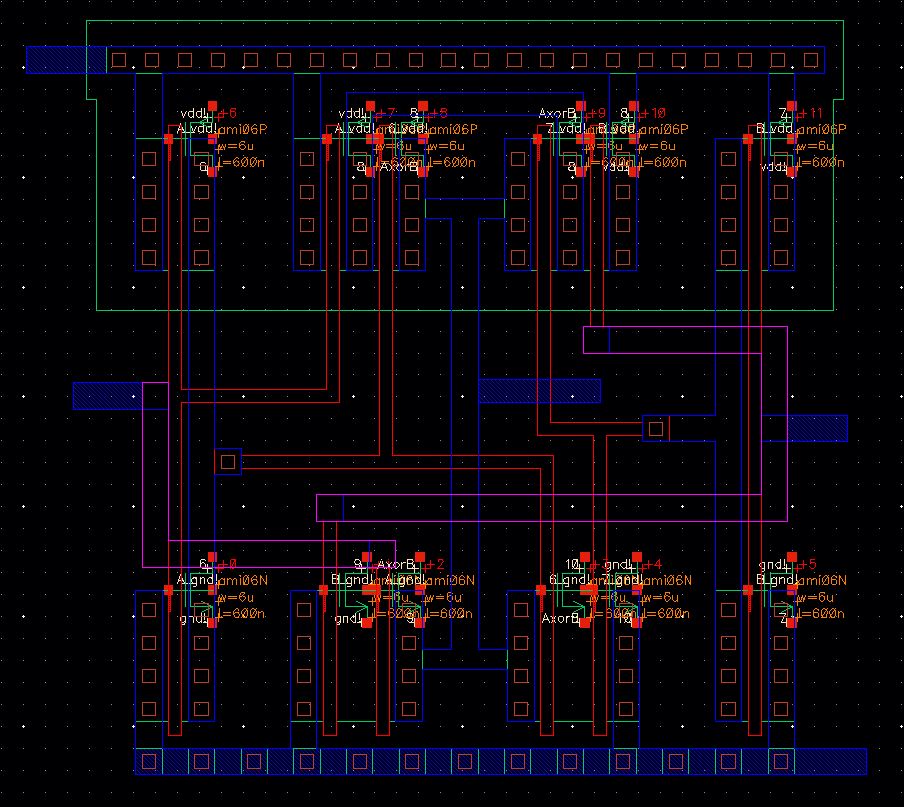

a 2 input NAND gate and XOR gate using 6u/0.6u MOSFETS (both NMOS and PMOS)

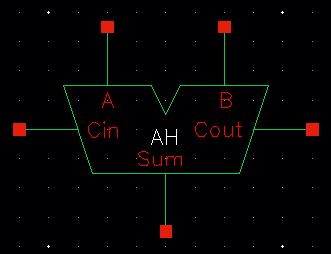

- Instantiate the layout created for NAND gate and XOR gate to create the layout of a FULL ADDER

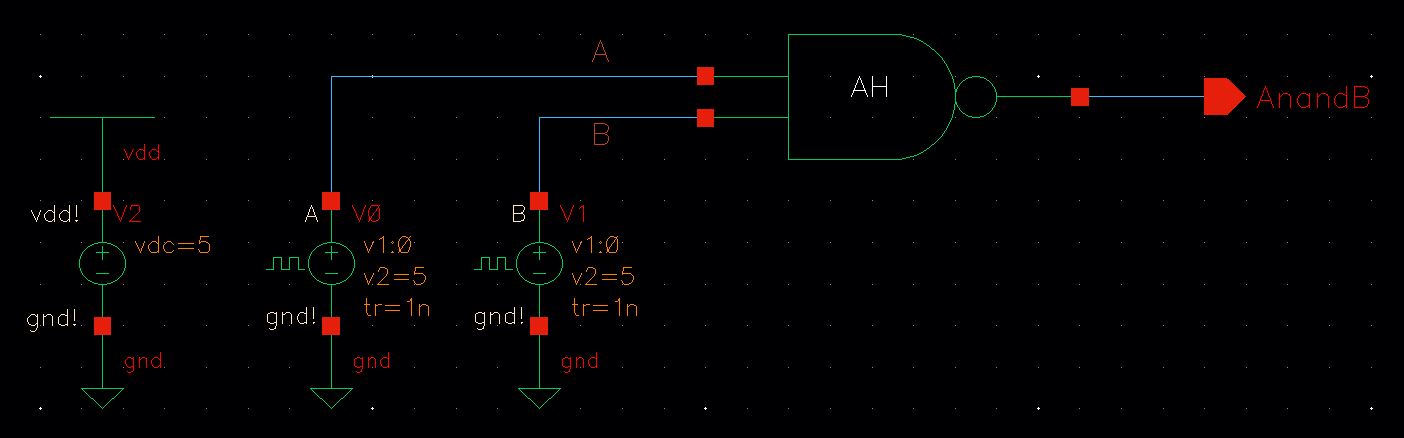

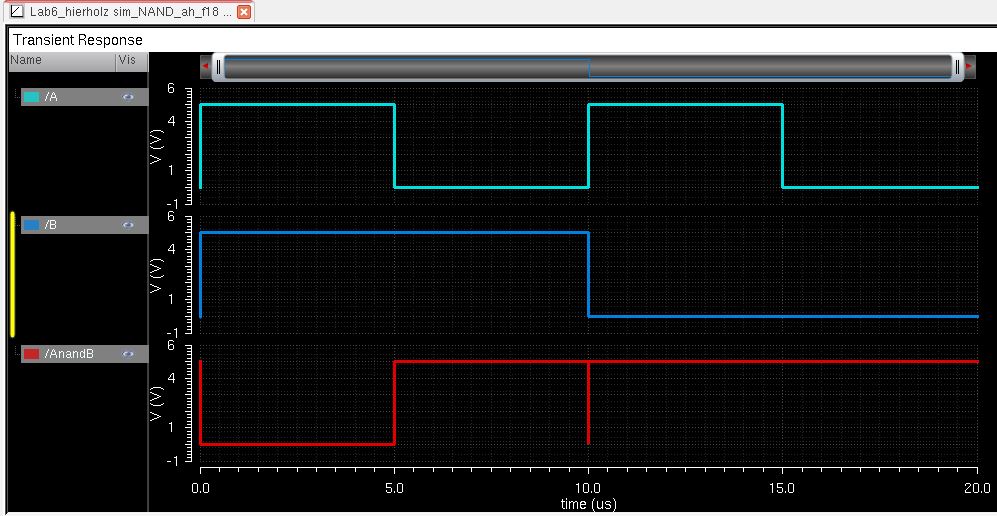

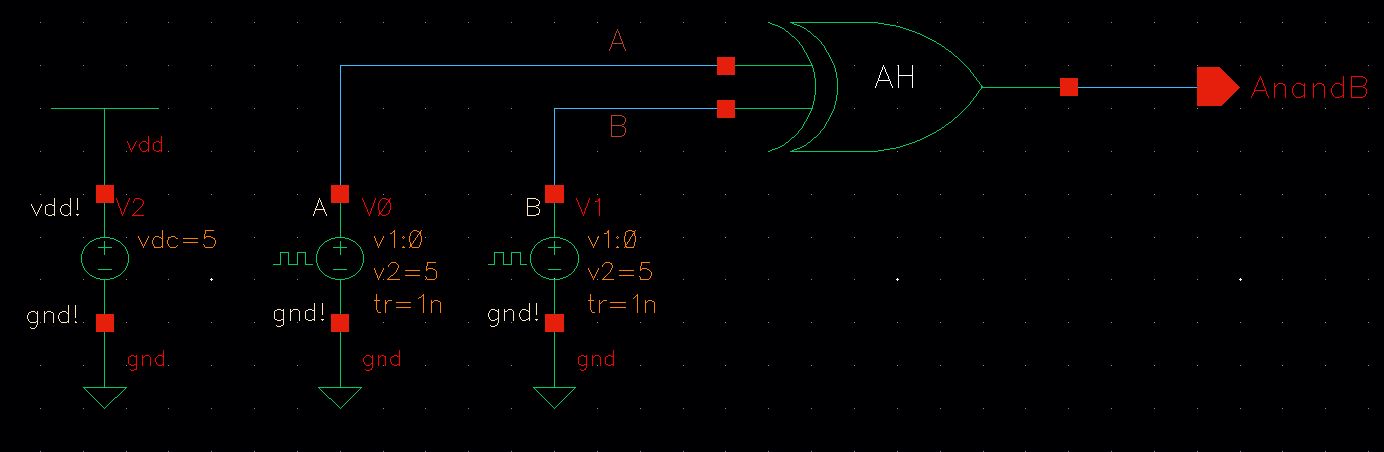

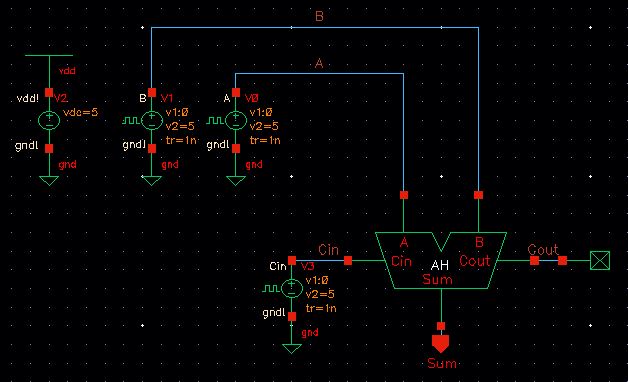

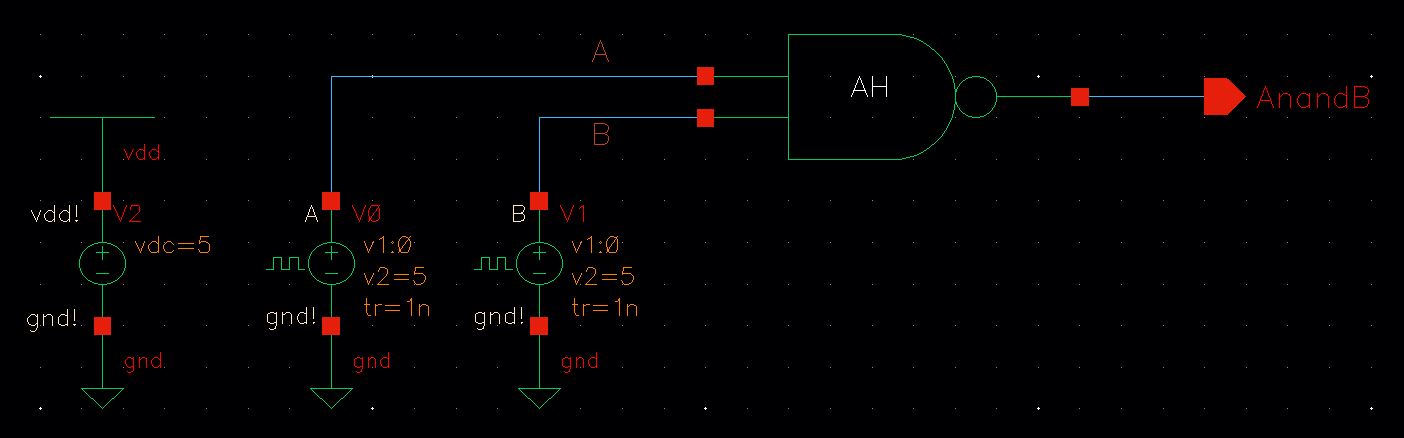

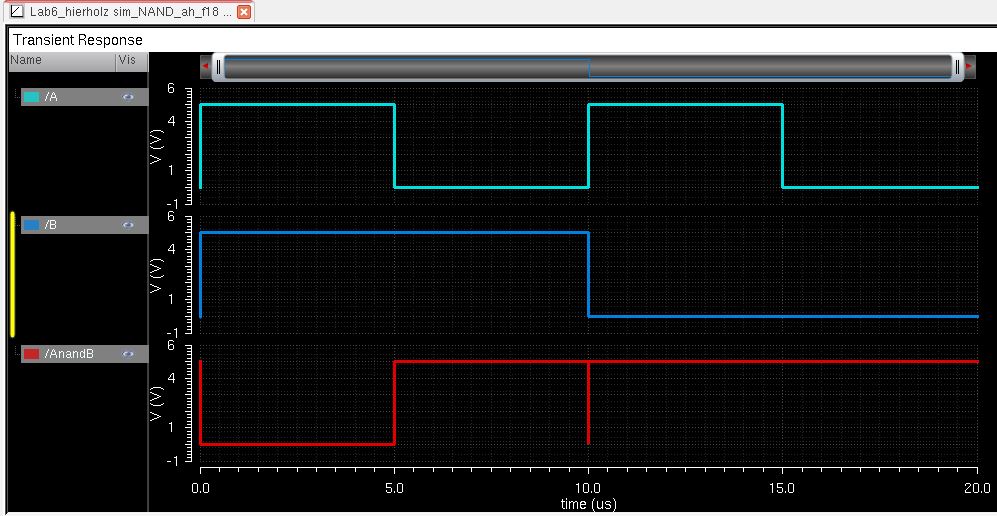

- Schematic to simulate the NAND gate

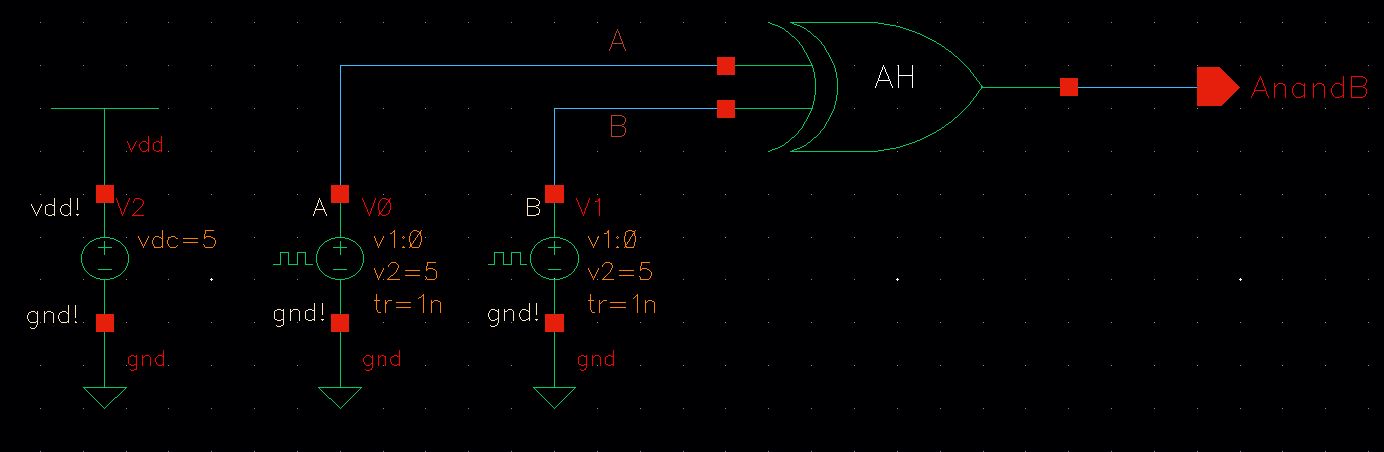

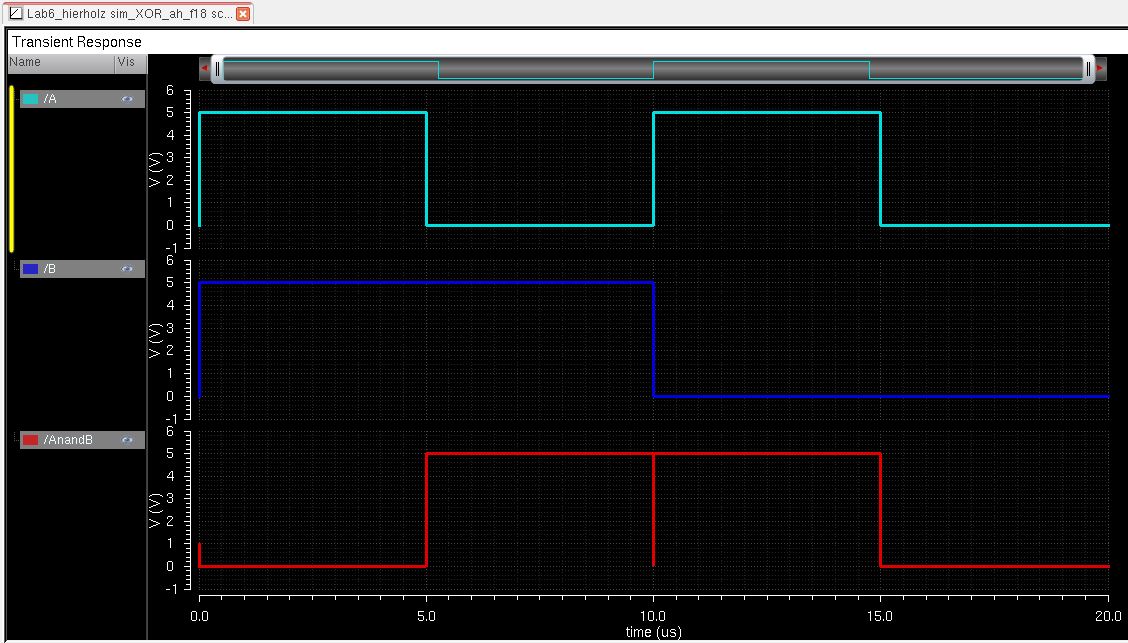

- Schematic to simulate the XOR gate

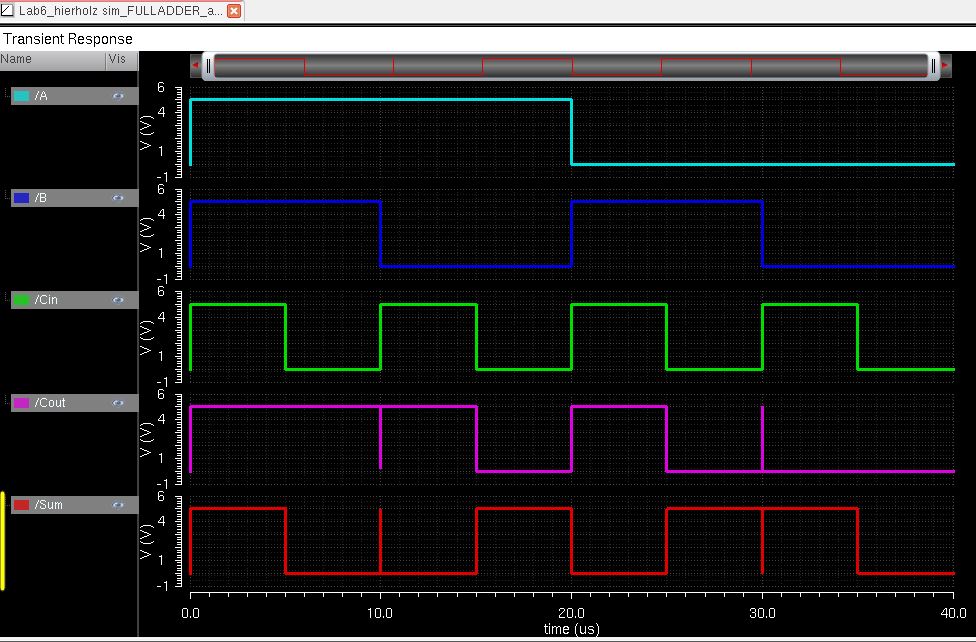

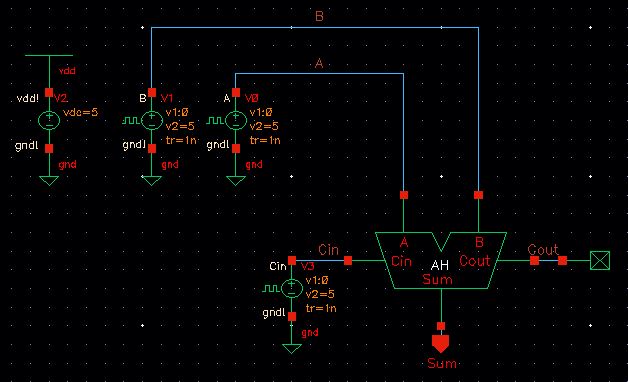

- Schematic to simulate the FULL ADDER

- The glitches on the simulation for NAND gate and XOR gate are caused by the

rise time and fall time of the inputs. Ideally, if the rise time and

fall time are ought to be 0, then the simulations should have no glitch.

The cells used to generate the images used on this webpage can be downloaded in Lab6_hie

Return to EE 421 Lab

Return to Student Lab Reports